La prossima generazione di comunicazone wireless non solo richiede una maggiore larghezza di banda alle frequenze più alte, ma richiede anche un po’ di tempo in più.

I ricercatori della Cornell University hanno sviluppato un chip semiconduttore che aggiunge un ritardo temporale necessario in modo che i segnali inviati su più array possano allinearsi in un singolo punto nello spazio e senza disintegrarsi. L’approccio consentirà a dispositivi sempre più piccoli di funzionare alle frequenze più elevate necessarie per la futura tecnologia di comunicazione 6G.

Il documento della squadra, “Ritardo quasi-vero ultracompatto per potenziare il wireless Capacità del canale”, è stato pubblicato su Nature. Bal Govind, uno studente di dottorato in ingegneria elettrica e informatica, è l’autore principale.

La maggior parte delle comunicazioni wireless attuali, come i telefoni 5G, funzionano a frequenze inferiori a 6 gigahertz (GHz). Le aziende tecnologiche mirano a sviluppare una nuova ondata di comunicazioni cellulari 6G che utilizzino frequenze superiori a 20 GHz, dove c’è più larghezza di banda disponibile, il che significa che possono fluire più dati e a una velocità maggiore. Si prevede che il 6G sarà 100 volte più veloce del 5G.

Tuttavia, poiché la perdita di dati nell’ambiente è maggiore alle frequenze più elevate, un fattore cruciale è il modo in cui i dati vengono trasmessi. Invece di fare affidamento su un singolo trasmettitore e un singolo ricevitore, la maggior parte delle tecnologie 5G e 6G utilizzano un metodo più efficiente dal punto di vista energetico: una serie di array di trasmettitori e ricevitori in fasi.

“Ogni frequenza nella banda di comunicazione subisce ritardi temporali diversi”, ha detto Govind. “Il problema che stiamo affrontando è vecchio di decenni: trasmettere dati a larghezza di banda elevata in modo economico in modo che i segnali di tutte le frequenze si allineino nel posto e nel momento giusto.”

“Non si tratta solo di costruire qualcosa con sufficiente ritardo, si tratta di costruire qualcosa con sufficiente ritardo in cui si abbia ancora un segnale alla fine”, ha affermato l’autore senior Alyssa Apsel, il professore di ingegneria IBM e direttore di ingegneria elettrica e informatica presso la Cornell Engineering. “Il problema è che siamo riusciti a farlo senza enormi perdite”.

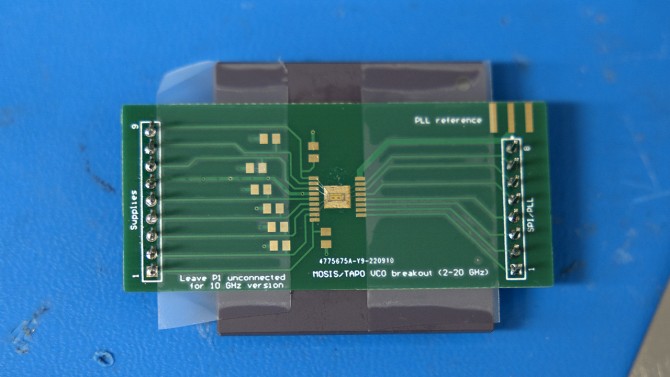

Il chip del computer progettato da Bal Govind e il suo team. Credito immagine: Ryan Young/Cornell University

Questo ritardo è stato precedentemente prodotto dai circuiti di sfasamento, ma questi possono gestire solo una certa quantità di dati. Questo è un problema particolare per i segnali a banda larga, in cui le frequenze più alte e quelle più basse possono cadere fuori fase, causando la sfocatura del segnale, un fenomeno noto come “squint del fascio”. E creare ritardi temporali in un minuscolo chip che possa essere inserito in uno smartphone non è un compito da poco.

“La maggior parte del modo in cui viene costruito il ritardo temporale è letteralmente utilizzando un lungo filo che consentirà di ritardare un segnale dal punto A al punto B. E abbiamo bisogno che quel ritardo sia regolabile in modo da poter reindirizzare questo raggio in posizioni diverse . Vogliamo che sia riconfigurabile”, ha detto Apsel.

Govind ha lavorato con il ricercatore post-dottorato e coautore Thomas Tapen per progettare un semiconduttore complementare a ossido di metallo (CMOS) in grado di regolare un ritardo temporale su una larghezza di banda ultra ampia di 14 GHz, con fino a 1 grado di risoluzione di fase.

“Poiché lo scopo del nostro progetto era quello di racchiudere il maggior numero possibile di questi elementi di ritardo”, ha affermato Govind, “abbiamo immaginato come sarebbe stato avvolgere il percorso del segnale in guide d’onda tridimensionali e far rimbalzare i segnali da esse per causare un ritardo, invece di diffondere lateralmente i fili della lunghezza d’onda attraverso il chip”.

Il team ha progettato una serie di questi riflettori 3D collegati insieme per formare una “linea di trasmissione sintonizzabile”.

Il circuito integrato risultante occupa un ingombro di 0,13 millimetri quadrati, più piccolo degli sfasatori, ma quasi raddoppia la capacità del canale, ovvero la velocità dei dati, degli array wireless convenzionali. E aumentando la velocità dati prevista, il chip potrebbe fornire un servizio più veloce, fornendo più dati agli utenti di telefoni cellulari.

“Il grosso problema con gli array a fasi è questo compromesso tra il tentativo di rendere queste cose abbastanza piccole da poter essere inserite in un chip e mantenerne l’efficienza”, ha detto Apsel. “La risposta a cui è arrivata la maggior parte del settore è: ‘Beh, non possiamo fare il ritardo temporale, quindi faremo il ritardo di fase.’ E questo limita fondamentalmente la quantità di informazioni che puoi trasmettere e ricevere. In un certo senso subiscono quel colpo.

“Penso che una delle nostre principali innovazioni sia proprio la domanda: è necessario costruirlo in questo modo?” Ha detto Apsel. “Se riuscissimo ad aumentare la capacità del canale di un fattore 10 cambiando un componente, si tratterebbe di un punto di svolta piuttosto interessante per le comunicazioni.”

Fonte: Università Cornell

Da un’altra testata giornalistica. news de www.technology.org